Apparently many DACs that use I2S architecture and related chipsets do not correctly convert 16 bit samples to 24 or 32 bit words prior to conversion. What measures are typically taken to correct this problem, as described below? Which chipsets and DAC architectures are more subject to it?

LSB extension error under I2S...

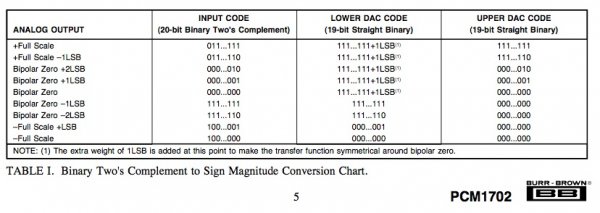

This problem started out during the transition from 32 FS (16 bit) to 64 FS clocking to accommodate sample lengths above 16 bits. Under the I2S spec, the LSB extension of a 16 bit sample to 24 or 32 bits is accomplished by simply adding bits set to zero. Seems reasonable by itself.

However, the samples are represented internally in 2s complement format, so in the case of positive numbers, one should extend the word length by adding the MSB (0) to the tail, and for negative numbers, adding the MSB (1) to the tail.

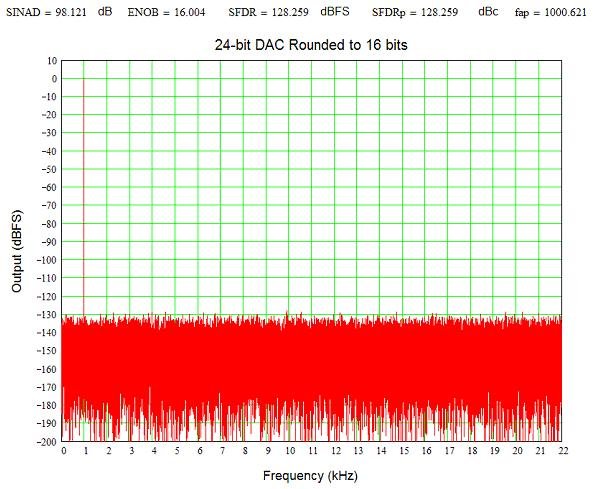

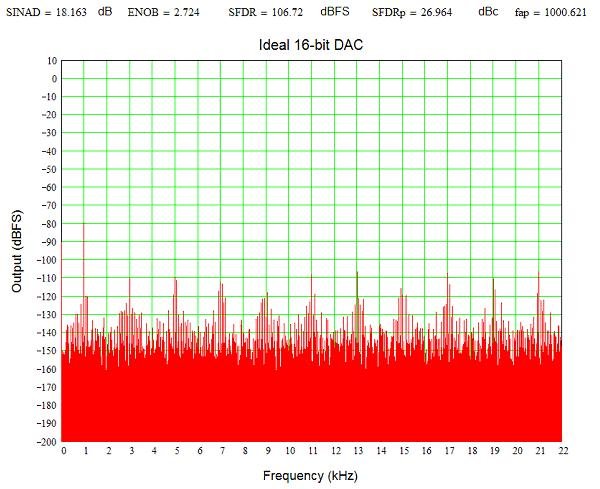

Thus, 50% of the time, namely for the negative samples as represented in 2s complement mode, the I2S convention is incorrectly forcing the LSBs to be 0, which introduces an erorr or distortion.

Some examples for a 16 to 32 bit extension (MSB on the left):

Full scale sample:

1111 1111 1111 1111 under I2S becomes 1111 1111 1111 1111 0000 0000 0000 0000

1111 1111 1111 1111 in correct 2s comp 1111 1111 1111 1111 1111 1111 1111 1111

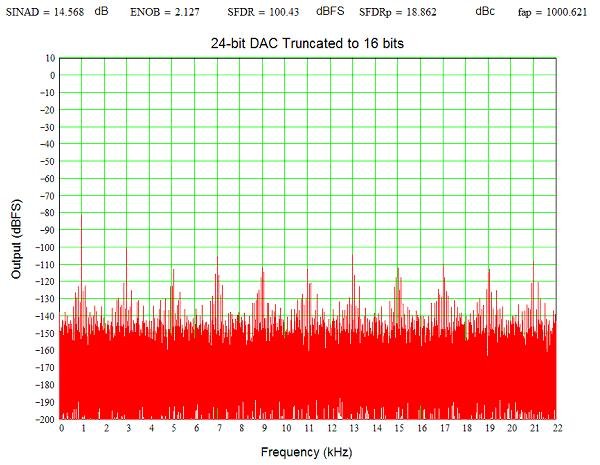

This error (the 16 LSBs set to 0 instead of 1) gives a distortion of 0.0015% of roughly -96 dB. (subtract incorrectly formatted sample from correctly formatted sample, divided by the correctly formatted sample).

For somewhat less than full scale sample:

1000 1111 1111 1111 under I2S becomes 1010 1111 1111 1111 0000 0000 0000 0000

1000 1111 1111 1111 in correct 2s comp 1000 1111 1111 1111 1111 1111 1111 1111

This time the error is about -66 dB.

For way less than full scale samples, say 0000 0000 0100 0000, the error is 3%, and it will rise up up to 99% for samples such as 0000 0000 0000 0001.

So we have an error that increases as the signal level decreases. Uh, oh.

LSB extension error under I2S...

This problem started out during the transition from 32 FS (16 bit) to 64 FS clocking to accommodate sample lengths above 16 bits. Under the I2S spec, the LSB extension of a 16 bit sample to 24 or 32 bits is accomplished by simply adding bits set to zero. Seems reasonable by itself.

However, the samples are represented internally in 2s complement format, so in the case of positive numbers, one should extend the word length by adding the MSB (0) to the tail, and for negative numbers, adding the MSB (1) to the tail.

Thus, 50% of the time, namely for the negative samples as represented in 2s complement mode, the I2S convention is incorrectly forcing the LSBs to be 0, which introduces an erorr or distortion.

Some examples for a 16 to 32 bit extension (MSB on the left):

Full scale sample:

1111 1111 1111 1111 under I2S becomes 1111 1111 1111 1111 0000 0000 0000 0000

1111 1111 1111 1111 in correct 2s comp 1111 1111 1111 1111 1111 1111 1111 1111

This error (the 16 LSBs set to 0 instead of 1) gives a distortion of 0.0015% of roughly -96 dB. (subtract incorrectly formatted sample from correctly formatted sample, divided by the correctly formatted sample).

For somewhat less than full scale sample:

1000 1111 1111 1111 under I2S becomes 1010 1111 1111 1111 0000 0000 0000 0000

1000 1111 1111 1111 in correct 2s comp 1000 1111 1111 1111 1111 1111 1111 1111

This time the error is about -66 dB.

For way less than full scale samples, say 0000 0000 0100 0000, the error is 3%, and it will rise up up to 99% for samples such as 0000 0000 0000 0001.

So we have an error that increases as the signal level decreases. Uh, oh.