Have you measured or listened to any proprietary FPGA converters?

Has Lynn measured or listened to anything except his own voice?

Have you measured or listened to any proprietary FPGA converters?

Well tbh it is a bit crude and may not show anything but may show some non-linearity, that is my caveatHaha, here's another one missing something. What trend do you refer to (or would like to see) ?

Has Lynn measured or listened to anything except his own voice?

Well tbh it is a bit crude and may not show anything

Have you measured or listened to any proprietary FPGA converters?

LynnOlson said:No, I haven't. I'm curious about the technology: I assume deglitching is non-trivial, and requires a well-designed sample-and-hold following the converter.

Peter I was not being critical so apologies if it looks like that.But Orb, I don't see where this is relevant. I mean, although I may use it as some reference here and there, this isn't about the NOS1, or ?

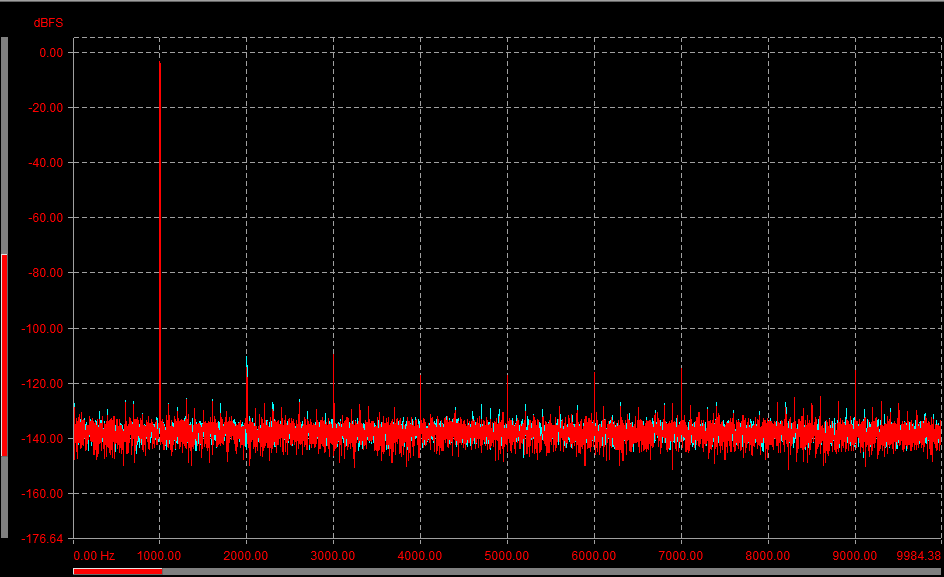

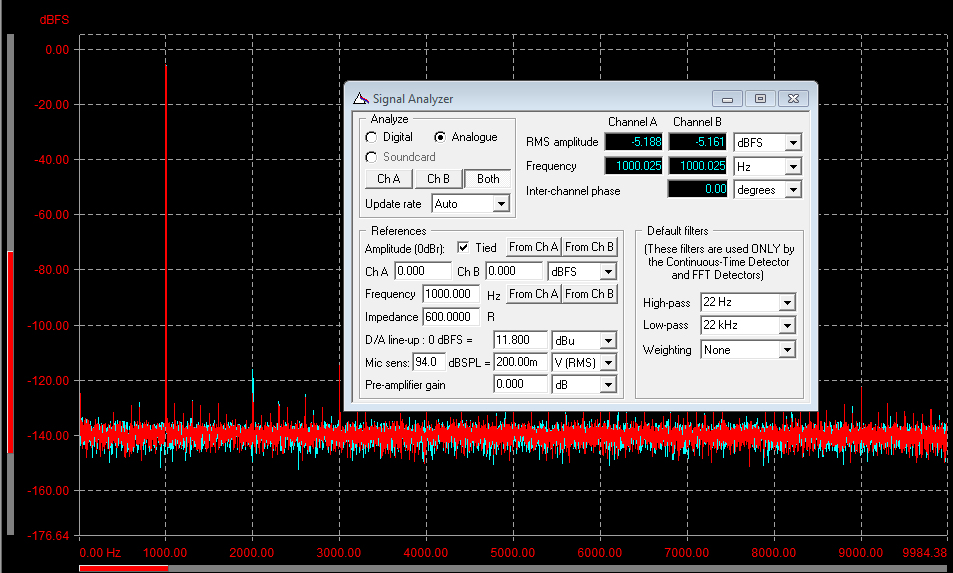

So before it is taken wrongly, my first graph was about how someone like me likes a straight noise line as a prerequisite and the second was in response to how averaging makes things look better.

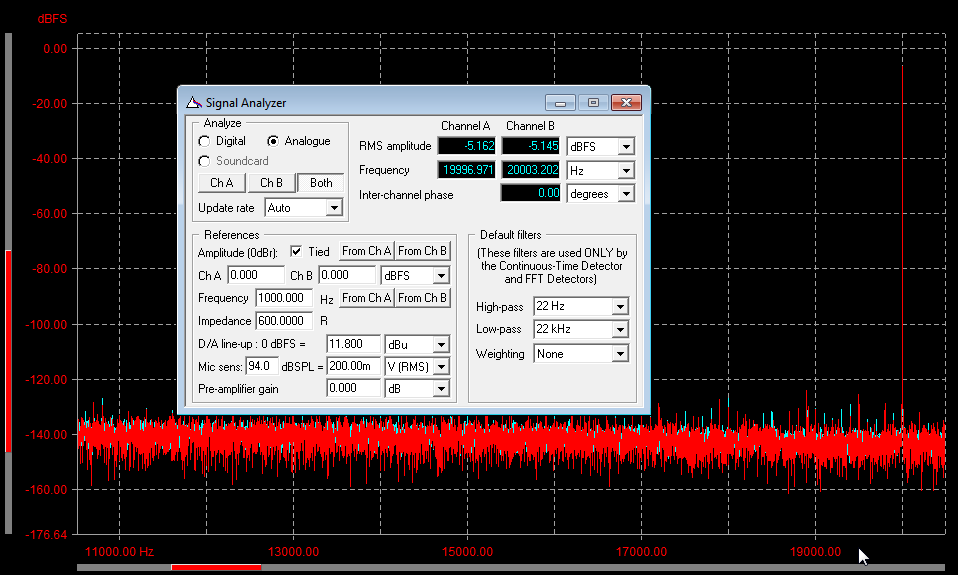

Now, supposed this was about PCM vs DSD and I could show plots of both for comparison and further discussion ... but I can't because then first I must have DSD going in the way I want it, and that is not the case. I wish it were.

I have thought about putting up some dirac pulses (these are pulses to the plus side only of one sample "width") which are sort of relevant to DSD which always still rings more, but firstly I thought it would be self-advertising and secondly such graphs don't come on their own. I mean, I can show those pulses which are 100% followed in analog (27KHz IIRC) but any pulse with infinite rise time (that's what it is) implies for infinite frequency and next we would be (no should be) in further analysis of the frequency band and what would happen with these infinite frequencies while actually we (still) talk about 16/44.1, though upsampled to 24/705.6 which right away makes them 16 samples long. Next I still can show these perfect pulses but captured by an SDM (of the analyser) which is 24/192 only and now nobody will understand what we're actually looking at. Could still be interesting for the thread, but IMHO not without doing the same for SSD which I can't.

And lastly, I never ever put out theoretical graphs (SPICEd let's say) because practice works out differently anyway. Take my analog-dither example from the earlier post ...

Regards,

Peter

All related to the subject for sure, Lynn, I hope you saw my (forum) PM to you from yesterday and I don't want to be intrusive, but I sure hope you can help me out.

Btw, no secrets or anything, but just not for the forum I think.

Thanks !

Peter

Hi Jim and good morning to all. Let's try to keep ad hominem attacks out of the morning posts please as they serve no useful purpose. Enjoy the rest of the day

FPGAs make good platforms for proprietary digital algorithms, but because of all the internally generated substrate noise are not useful for the analog portion of the conversion; that must be done externally with devices on a separate substrate. In the AD1955 dac, ADI isolates the current switches which perform the conversion to the 'analog' signal in a separate well with its own substrate ground pin. Bob Adams told me once that they spent a lot of time on this isolation problem to get that chip's level of performance.

With careful design, a simple one bit converter for DSD could be done - a single DMOS switch with glitch cancellation. For a multi-bit converter it's something of a nightmare, because the glitch energy depends on the number of actual current switches changed for each sample - and which ones follow which others! That's why Burr Brown forgo the degliching in favor of low glitch energy. Even so, that still represents much of the error in both of their respected NOS dacs.

Sample and hold's add their own coloration, even if their glitch energy is cancelled.

44.1 176.4.png)

FFT.png)

FFT.png)

| Steve Williams Site Founder | Site Owner | Administrator | Ron Resnick Site Owner | Administrator | Julian (The Fixer) Website Build | Marketing Managersing |